Enabling the use of high-performance chips in safety-critical domains such as automotive, Space, and the like challenges the verification and validation of the system as a whole, and the deployment of appropriate safety measures to mitigate and manage errors. While there have been attempts to design high-performance chips where those issues, namely verification, validation and deployment of safety measures, are no more complex than in simpler designs by construction, they have not been matured and/or adopted due to multiple reasons such as limited performance, and lack of reuse of legacy IP. In this context, deploying features for verification, validation and safety measure realization while preserving legacy IP “as is” and performance unaffected becomes of paramount importance.

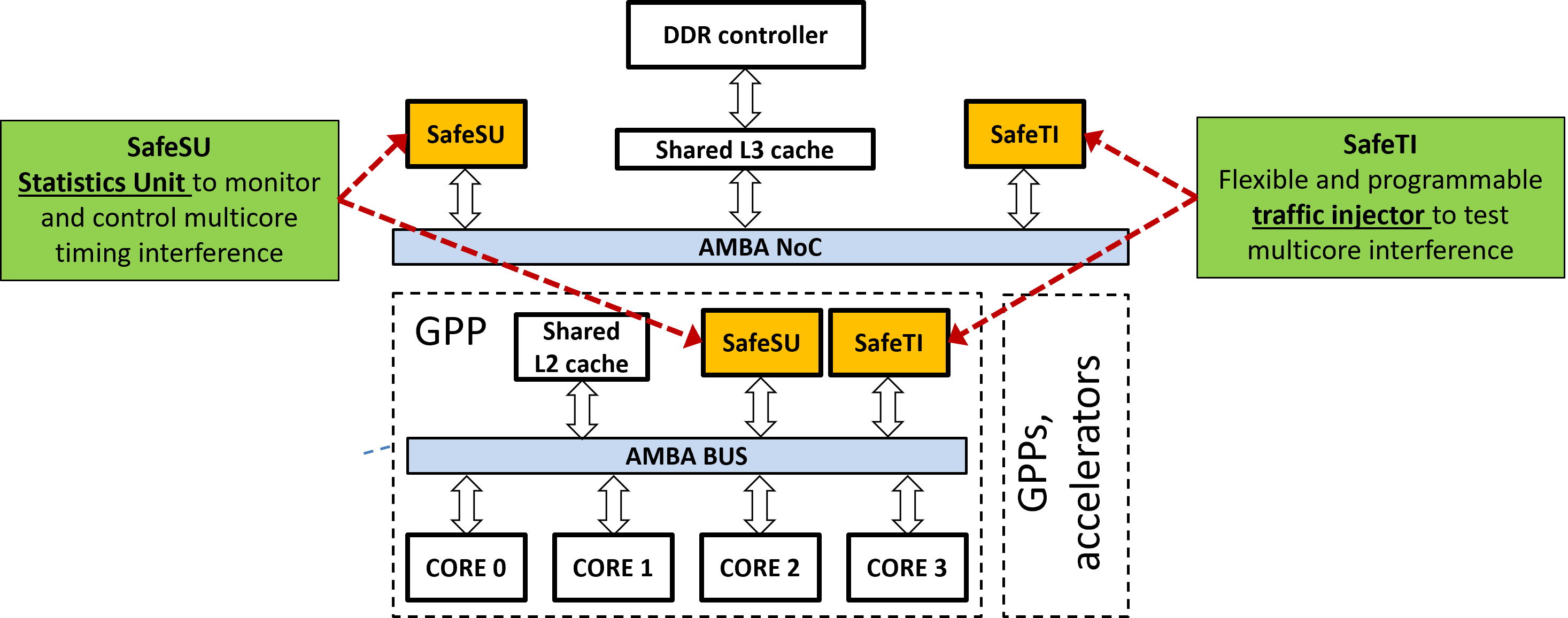

BSC, as part of its work in ISOLDE, is enhancing, integrating and maturing two components providing observability and controllability capabilities, as needed for verification, validation and safety measure realization. In particular, BSC contributes with the SafeSU statistics unit and the SafeTI traffic injector, which are being extended with additional capabilities to monitor components and inject traffic even in a different System-on-Chip (SoC), will be integrated as part of a Safety Island to interact with high-performance chips, and will undergo a strict validation process and include appropriate safety manuals. By providing out-of-the-band on-chip traffic monitoring and injection, misbehavior and resource abuse will be easier to be detected and reproduced, and safety measures deployed to avoid failures related to such misbehavior and resource abuse.

Both BSC components, the SafeSU and SafeTI, are specifically integrated in RISC-V SoCs and released with open source permissive licenses to ease their adoption and the development of European safety-relevant RISC-V SoCs with high-performance capabilities.