The gap between design and implementation is a bottleneck in hardware development. With Register-Transfer Level (RTL) generation often neglecting the physical implementation constraints tapeouts can delayed or even broken. As RTL-models – sometimes already called RTL-programs – are said to be the way for technology independent digital designs this challenge is often despised. Even more, re-use of RTL-IPs is claimed to be the way to close the digital design gap, that is the disparity between the growth of manufacturable transistors and the ability to design circuits and systems that effectively utilize them.

However, as the physical reality is ignored the re-use rate is lower than planned. When digging deeper, following four major reasons can be identified. First, different features and feature variants of an IP are needed to fully cover the potential of re-use and to avoid modifications in code that is claimed to be re-usable. Examples include the number of channels in communication-IPs or timer-IPs, the sizes of objects used for holding addresses or data, or slight variations in implementation. Second, the soft-IP must operate in different domains and under different conditions. Therefore, it is required to provide special features, e.g., safety, security, or (self-) test features. Third, even though RTL code can conceptually be synthesized to any semiconductor target technology, some code items in the RTL code such as instantiating clock gates, memories, or pads remain technology-specific. Further, meeting timing constraints may partially require to implement functionalities differently. Last but not least – and fourth - FPGA prototypes are increasingly used for validation purposes, making it essential to ensure the seamless mapping of RTL code to both ASIC and FPGA technologies.

All these challenges require the RTL code to follow different and sometimes partially contradicting requirements. One approach to tackle these challenges is making use of so-called generic IPs that can be configured with generics (VHDL) or parameters (SystemVerilog). However, generic-IPs can support different object sizes but do not provide features like optional ports or flexibility in instantiating components. To enhance adaptability, generator-based approaches have been developed that leverage partly hardware generation languages (HGL). VHDL and SystemVerilog configurations conceptually can (re-)configure component instantiations but this feature is not supported by synthesis tools.

As the HDL and HGL approaches cover the mentioned challenges only to some extent the Model-Driven Architecture (MDA)-based code generation, an iterative flow of model refinements and final un-parsing, is the way of choice to generate RTL and other collaterals in a highly reusable way. With the MDA inherent transformation and generator approach, RTL code can be provided in a significantly more flexible manner, supporting facets such as feature dependent ports or port properties. In addition, MDA promotes the idea of creating abstract models that describe system functionality, which can then be automatically or semi-automatically transformed into RTL code. This approach is appealing due to its promises of efficiency, reusability, and reduced human error. From a high-level perspective, re-use of code is replaced by re-using transformation and generation utilities.

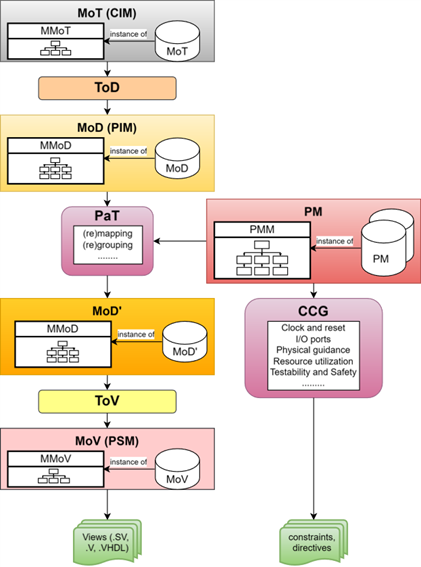

The picture on the left gives an overview on the process. Generation that starts with a Computation Independent Model (CIM). We call this model Model of Things (MoT) as only things, their attributes and relations are defined. This model is translated in a Platform Independent (Implementation) Model, which we call Model of Design (MoD) as it includes already most of the design aspects. With a transformation, the MoD is migrated to a MoD’ which is still platform independent put easier to translate to the target platform. The target platform specific code is finally reached by translating to a Platform Specific Model (PSM), which we call Model of View as it closely relates to the target formalism. The MoV is finally unparsed to the target code. As hardware platforms are inherently heterogeneous and often optimized for specific use cases, platform awareness is an essential requirement for getting the best results. For example, the priority for a CPU-centric SoC would be high clock speeds and general-purpose processing. For FPGA platforms, however, parallelism and reconfigurability are keys. Defining and considering metrics such as timing constraints, resource availability, and power considerations, highly influence the power, performance, and area (PPA) attributes of a design.

PAF, the Platform Aware Flow, is a systematic platform-model (PM)-based approach aimed at unlocking the full potential of MDA based RTL generation by enhancing the platform awareness while preserving the abstraction advantages. The approach leverages a Platform Model (PM) to improve the overall chip design flow by enabling the generation of platform-aware RTL, along with platform-specific constraints and directives whilst keeping the generator well structured. These enhancements guide backend tools to achieve better quality results, facilitate faster design closure, and incorporate testing and safety features tailored to the target platform. This approach bridges the gap between RTL and implementation through increasing automation. It also ensures that the resulting chips meet testability and safety requirements.

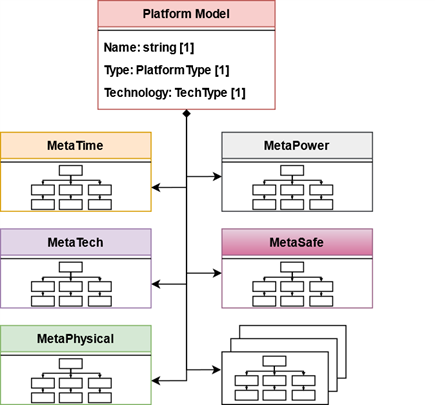

A sketch of a Platform Model is shown on the left. It is composed of aspect specific sub-models besides platform descriptive attributes. These sub-models steer the PIM-to-PIM’ and PIM’-to-PSM transformations. Each of that covers other aspects as timing and power, technology specific components or safety specific properties.

The key to the PAF-approach is to introduce platform models as conceptually foreseen by the MDA vision. Second pillar is a flexible engine that interprets platform models and modifies design models through a set of fundamental editing operations, resulting in RTL code that is tailored for the target platform. We further utilize the platform models together with the design model to generate other collaterals. We have demonstrated the effectiveness of our approach through qualitative analysis and quantitative results, ultimately showing a significant 73% reduction in code generation effort for industrial-grade designs. By bridging the gap between design and implementation, our Platform-Aware RTL Generation flow has the potential to revolutionize the hardware development process as well as enabling faster time-to-market, improved design quality, and reduced development costs.