Watch now the lightning talk by Florian Wohlrab regarding the Contribution towards European sovereignty for embedded processors in ISOLDE and TRISTAN at RISC-V Summit Europe 2025.

In the ISOLDE Project, IMT contributes to both algorithm development and digital designs. We are adapting split-radix algorithms for hardware acceleration of the Fast Fourier Transform (FFT) used in signal processing and high-performance computing, as well as for Number Theoretic Transforms (NTT) applied in post-quantum cryptography. Additionally, we are designing a SIMD/Vector accelerator optimized for matrix operations and a high-bandwidth, multi-port scratchpad memory.

At IMT, we utilize FFT for specially designed coded sequences in acoustic sensors, enabling longer acquisition times to achieve a better signal-to-noise ratio. A hardware-accelerated FFT will allow IMT to dynamically adapt these coded sequences to time-varying environmental conditions. Additionally, we employ FFT to solve partial differential equations on periodic cells, facilitating the estimation of macroscopic properties from 2D/3D images of microstructures. These applications span a broad range of physical phenomena, including two-phase flow prediction in porous media, the dielectric behavior of biological cells, and anisotropic crystal plasticity in metals and metallic alloys. This creates opportunities for real-time integration of micro-macro predictions into quality assessment and control systems.

Separately, we investigate algorithms for the Number Theoretic Transform (NTT), the counterpart of the FFT for integer arithmetic in finite fields, with applications in fast polynomial multiplication within finite polynomial rings. This operation is among the most computationally and energy-intensive tasks in Post-Quantum Cryptography (PQC) based on Ring/Module Learning With Errors. A challenge is that only a limited selection of finite rings supports NTT. While some PQC algorithms are specifically designed around NTT-friendly choices, others deliberately avoid them to reduce the attack surface. Our work focuses on developing universal NTT algorithms, leveraging complex transforms for generalized Mersenne primes and real transforms for powers of Fermat primes.

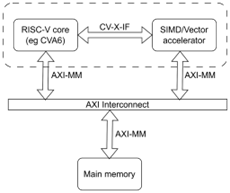

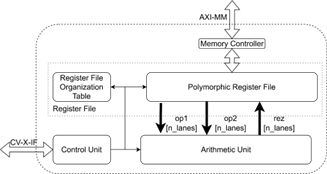

IMT also contributes to the development of a SIMD/Vector accelerator, a tightly coupled hardware extension for RISC-V cores. This accelerator features software-defined two-dimensional registers and enhances matrix operations, which are widely used in Artificial Intelligence (AI), particularly in Machine Learning (ML). It is integrated with the main core via the RISC-V extension interface, specifically the new CoreV-eXtension-Interface (CV-X-IF).

The proposed accelerator has two interfaces: one connecting to the main core and another to the main memory which is also used at unloading memory operations from the core. The new CV-X-IF interface for RISC-V cores enables the extension of the Instruction Set Architecture (ISA) with new opcodes and provides direct access to core registers, significantly simplifying the design of tightly coupled accelerators. Figure 1 illustrates the accelerator’s role in the system and its interactions with other components.

Figure 1. SIMD/Vector accelerator: Interfaces and internal organization

The National Institute for R&D in Microtechnologies IMT-Bucharest (Romania) is a non-budgetary public research unit. The main research fields are in closed connection to four Key Enabling Technologies: micro-nanoelectronics, photonics, nanotechnology and advanced materials.

The research centers that compose IMT are MIMOMEMS : European Research Centre of Excellence (Micro- and nano-systems for radiofrequency and photonics), CNT-IMT: Center of Nanotechnologies, CINTECH: Research Centre for integration of technologies (micro-nano-biotechnologies) and CENEASIC: Research Centers for nanotechnologies devoted to advanced carbon based integrated nanosystems and nanomaterials. The latter is also one of the fabrication facilities inside IMT, alongside MINAFAB: Center for Micro and NAnoFABrication.

The laboratories inside the institute that drive innovation across various fields include microsystems for biomedical and environmental applications, nanobiotechnology, molecular nanotechnology, micro-nano photonics, micromachined structures, microwave circuits and devices, as well as simulation, modeling, and reliability. With a team of 200 experts in electronics, computer science, physics, chemistry, and biology, IMT has participated in over 100 European projects (Horizon Europe, H2020, FP7, FP6, bilateral cooperation). As a result, it has become a recognized partner in numerous multidisciplinary consortia and networks.

In this page the ISOLDE public deliverable reports are published and available for download. They are structured in-line with the overall ISOLDE structure.

The requirements and specifications will be established early in the project in WP1 and will drive the 3 development WPs. The focus of WP2 is the development of foundational cores including core specific infrastructure IPs as used in the memory hierarchy, such as high-performance caches, NoCs and multi-core support. The focus of WP3 is domain specific accelerators for applications such as cryptography, machine learning and vector units for high-performance. All the work on application SW, tools, compilers and automation will take place in WP4. To ensure that the components will work together and can be used to build systems, multiple demonstrators in 4 domains will be built, and these are the focus of WP5. There are many administrative and legal challenges that are specific to developing complex SoCs that integrate open-source blocks that can have different licensing terms. It is important that these be fully addressed, and these constitute a key aspect of WP6, which also includes the exploitation and dissemination activities. Finally, WP7 covers the project management, including the coordination between partners and reporting to the commission.

Note that only the public deliverables are listed on this page. Only public deliverables approved by the Chips JU can be downloaded from this page. If you would like more information about a specific deliverable report, please feel free to contact us at info![]() isolde-project [dot] eu.

isolde-project [dot] eu.

30 November 2023

The purpose of this document is to collect the initial requirements for the demonstrators in the chosen application areas (Automotive, Space, Smart home, IoT), as worked out in T1.1.

It contains both functional and non-functional requirements, at least from the following subjects: architecture (components, interfaces, accelerators), measurable metrics and goals (performances, power consumption, radiation tolerance, security metrics to be used), SW requirements (stacks, tools, system SW features, SW for demonstrators use cases), and standard to be used/considered.

The main goal of this document is to have a sound starting basis for further iteration and refinement in the different WPs of the project. Some of the requirements have already been worked out in full detail, while others still contain some open questions or issues to be finalized. For example, regarding verification and validation, further refinement and updates are still needed. Such activity will be carried out in D1.3 where the final requirements will be frozen.

This document supports the technical report associated to the deliverable D1.1 "Demonstrators Requirements and Specifications" reporting to the WP1 "Requirements and Specifications" leader (E4 Computer Engineering S.p.A.) for the Project ISOLDE.

The document is prepared in the frame of the Task 1.1 – Collection of requirements of the demonstrators & high-level SoCs specifications (WP1).

30 November 2023

This Deliverable reports an initial list of requirements and specifications for the various components developed in the context of the ISOLDE project relative to core architecture, hardware and software modules. In addition, this Deliverable provides a first indication about the IP corresponding to each component. A consolidated version of this document will be produced as a follow-up Deliverable D1.4. All partners involved in Tasks 1.2, 1.3 and 1.4 contributed to this Deliverable.

21 May 2024

The purpose of this document is to collect the requirements for the project demonstrators in the chosen application areas (Automotive, Space, Smart home, IoT), as worked on in T1.1 "Collection of requirements of the demonstrators & high-level SoCs specifications" (M1-M12). The base for this document is the information contained in D1.1 "Demonstrators requirements and specifications", and D1.2 "Requirements and specifications on architecture, hardware and software modules and IPs", which has been updated following the progress of the work done in WP2, WP3, WP4 and WP5 adding also more detail on IPs implementation as well as the definitions of the architectures of the planned demonstrators. D1.3 is the final outcome of T1.1.

The document contains both functional and non-functional requirements for the following subjects: architecture (components, interfaces, accelerators), measurable metrics and goals (performances, power consumption, radiation tolerance, security metrics to be used), SW (stacks, tools, system SW features, SW for demonstrators use cases). There are also references, where significant, to standard to be used/considered.

D1.3 includes an overview of each demonstrator, whose objectives and proposed architecture are described in more detail in D5.1 "Description of demonstrators architecture" (due M12, same as this document), to contextualize the requirements and the verification strategy attached to them.

This document supports the technical report associated to the deliverable D1.1 "Demonstrators Requirements and Specifications" reporting to the WP1 "Requirements and Specifications" leader (E4 Computer Engineering S.p.A.) for the Project ISOLDE.

27 January 2025

This document describes the work performed within ISOLDE WP2 Open-Source Foundation Cores. WP2 will develop IPs that will be delivered through internal repositories during the work and finally through the ISOLDE virtual repository. WP2 progress will be reported through updates of this report that will be issued as document deliverables D2.2 (M18) and D2.3 (M33).

The requirements and specifications for the work to be performed is established in WP1. At the time of issuing this report, much of the work to be carried out in WP2 is still in the specification or planning stage.

13 November 2024

This document describes the work performed within ISOLDE WP2 Open-Source Foundation Cores. It is the update of document deliverable D2.1 (M6). WP2 is developing IPs that will be delivered through internal repositories during the work and finally through the ISOLDE virtual repository. WP2 progress will be reported through update of this report that will be issued as document deliverable D2.3 (M33).

The requirements and specifications for the work to be performed is established in WP1. At the time of issuing this report, much of the work to be carried out in WP2 is now in the implementation stage.

21 May 2024

The ISOLDE project aims to create high-performance processing systems and platforms targeting different use cases (space, automotive, smart home, cellular IoT) based on the free, open-source RISC-V instruction set architecture. This document defines the initial architecture of the required hardware modules and extensions (called extensions in the following) developed within the work package WP3 "Accelerators and Extensions" of the ISOLDE project to reach this goal. It encompasses contributions from all tasks (T3.1 to T3.6) and partners within WP3.

The extensions described in this report are grouped into different domains matching the scope of the different tasks within WP3:

For each extension, this document contains general information (type, dependencies, and license) and an initial architecture description giving a first insight into its purpose and internals. These initial architecture descriptions answer core questions about each extension:

WP5 "Use Cases and Demonstrators" will combine the foundational cores developed by WP2 "Open-source Foundation Cores" and selected features from WP3, building diverse demonstrators (space, automotive, smart home, cellular IoT) that highlight benefits and opportunities enabled by individual extensions. Further, WP4 "System Software, Development Tools and Automation" will provide the required software support (e.g., toolchains, operating system support, drivers). Hence, the contributions of this deliverable are crucial for further collaboration with these work packages. In the context of WP3, this deliverable is the basis for the follow-up deliverables covering the prototype and final implementations of the extensions (D3.2, D3.3 in M24 and D3.4, D3.5 in M33). The components described in this deliverable are aiming at different maturity levels and aiming for different certifiability. Further, this document represents the first iteration of the architecture definitions and hence not all contributions have the same level of maturity. A short survey of the ISOLDE partners for certification intentions (including WP3 components) will be later provided by SYSGO as part of WP1 work.

29 April 2025

The ISOLDE project aims to create high-performance processing systems and platforms targeting

different use cases (space, automotive, smart home, cellular IoT) based on the free, open-source

RISC-V instruction set architecture.

This documents refine the architecture and describe the prototype implementations of the hardware

modules related to safety and security, previously introduced in Deliverable D3.1. These

modules have been developed within the work package WP3 "Accelerators and Extensions" of

the ISOLDE project, more particularly in tasks T3.1 and T3.3.

The extensions described in this report are grouped into different domains matching the scope of

some different tasks from WP3:

For each safety / security extension, this document contains refined architecture description since

deliverable D3.1, reminding the purpose of the extension, where in the system is it integrated,

and which other systems it is connected to. We then provide a more detailed description on

the hardware module internals, describing the prototype that allow the hardware module to be

evaluated / verified.

WP5 "Use Cases and Demonstrators" will combine the foundational cores developed by WP2

"Open-source Foundation Cores" and selected features from WP3, building diverse demonstrators

(space, automotive, smart home, cellular IoT) that highlight benefits and opportunities enabled by

individual extensions. Further, WP4 "System Software, Development Tools and Automation" is

providing the required software support (e.g., toolchains, operating system support, drivers).

Hence, the contributions of this deliverable are crucial for further collaboration with these work

packages. In the context of WP3, this deliverable is the basis for the follow-up deliverable covering

the final implementations of the extensions (D3.4, D3.5 in M33). The components described in

this deliverable are aiming at different maturity levels and aiming for different certifiability.

30 April 2025

Deliverable D3.3 presents the prototype implementations of hardware accelerators developed

within Work Package 3 (WP3) of the ISOLDE project. These components target key computational

domains—including AI/ML, cryptography, signal processing, and virtualization—supporting

the project’s goal of building customizable and efficient RISC-V-based platforms for embedded

applications.

The deliverable includes over 20 synthesizable and evaluable IPs, organized across the following

categories:

Each IP is described via a standard template ("IP Card") detailing functionality, architecture, integration

interface, maturity level, and evaluation results (e.g., FPGA/ASIC synthesis, performance,

power).

This deliverable represents a transition from design to validated prototype, supporting downstream

integration with WP5. It forms the technical baseline for final implementation deliverables D3.4

and D3.5.

13 May 2024

This Deliverable reports the proposed architectures of the four Demonstrators (Space, Automotive, Smart Home, Cellular IoT) in four separate sections, as well as providing a more detailed description of the use case applications. A consolidated version of the Demonstrator requirements is instead provided in Deliverable D1.3, written at the same time. All partners involved in WP5 contributed to this Deliverable.

22 May 2024

This document is prepared in the frame of the Tasks 6.2 "Outreach and Dissemination" and Task 6.3 "Exploitation" – (WP6).

Since ISOLDE is an open-source project, dissemination is essential for many reasons. Firstly, for maximizing impact: open-source projects thrive on collaboration and community engagement. Dissemination allows project outcomes and innovations to reach a wider audience, increasing the potential for adoption and utilization. By sharing knowledge, code, and documentation, open-source projects can have a broader impact and contribute to solving real-world problems. ISOLDE is aimed to build and contribute to the Reduced Instruction Set Computing (RISC)-V ecosystem in Europe, and although we have many stakeholders available in the project, outreach to external stakeholders is essential to reach maximum impact. This will also be done in close cooperation with the TRISTAN project which has similar ambitions. ISOLDE differentiates from TRISTAN by focusing on "stronger" application processors as to the "smaller" processors targeted by TRISTAN.

A well-designed dissemination approach will facilitate new collaborations. By making ISOLDE results publicly available, it becomes easier for others to contribute, provide feedback, and build upon the work done. This collaborative approach fosters innovation and accelerates the development of new ideas and solutions. Extension of the ISOLDE network to other stakeholders in open-source will help to increase the community and that will foster acceleration of innovations within ISOLDE.

Finally, we strongly believe that by getting feedbacks during dissemination activities from the RISC-V community, the quality and reliability of the IP blocks developed in ISOLDE will be improved. Although ISOLDE targets to achieve a Technology Readiness Level (TRL) 6, a large stakeholder community can help identify bugs, improve functionality, and enhance the overall quality and reliability of the project. This deliverable describes through the proposed dissemination plan the methodology and tools to be used to generate maximum dissemination impact.

Beyond dissemination, exploitation is also of crucial importance. Exploitation is a must-have to ensure that results end up in the market in a successful way. ISOLDE primarily aims to enhance and mature the European RISC-V ecosystem and to support the ongoing shift towards open source methodologies and solutions in that context. Therefore, one of the results will be exploited via open-source and others via different licensing mechanisms. Some of the results will remain company-confidential and will be exploited by individual partners on the market. This first version of the exploitation plan has been drafted at the end of year 1 of ISOLDE. During this stage initial technical results have been achieved, but technical maturity still needs to increase. The information in Section 3 of this document supplements exploitation information in Part A and Part B of the Grant Agreement and includes contributions from partners with addenda thereto.

28 May 2024

This document describes the work performed within ISOLDE WP6 – Open – source Strategy, Business Models, Exploitation and Dissemination in Task 6.1.

A consolidated version of this Deliverable provides info and can demonstrate that networking within the realm of RISC-V, open-source technology, embedded processor development, and SoC application design can greatly expand ISOLDE reach and impact.

25 November 2024

This document describes the work performed within ISOLDE’s Task 6.2: Outreach and dissemination from WP6 and continues the legacy of deliverable D6.1: Initial Plan on Dissemination & Exploitation.

This document outlines a well-defined and customized ISOLDE dissemination and communication plan, highlighting the use of the different dissemination tools, strategies, and planned activities as of October 2024 used by the consortium. These include not only individual work performed by partners, but also joint actions. To achieve this, the dissemination strategy aims to raise awareness and interest in the solution developed during the project among the different audiences.

Since ISOLDE is an open-source project, dissemination is essential for many reasons. Firstly, for maximizing impact: Open-source projects thrive on collaboration and community engagement. Dissemination allows project outcomes and innovations to reach a wider audience, increasing the potential for adoption and utilization. By sharing knowledge, code, and documentation, open-source projects can have a broader impact and contribute to solving real-world problems. ISOLDE is aimed to build and contribute to the RISC-V ecosystem in Europe, and although the consortium has many stakeholders available in the project, outreach to external stakeholders is essential to reach maximum impact. This will also be done in close cooperation with the TRISTAN project, which has similar ambitions.

A well-designed dissemination approach will facilitate new collaborations. By making ISOLDE results publicly available, it becomes easier for others to contribute, provide feedback, and build upon the work. This collaborative approach fosters innovation and accelerates the development of new ideas and solutions. Extension of the ISOLDE network to other stakeholders in Open Source will help to increase the community and that will foster acceleration of innovations within ISOLDE.

Finally, the consortium strongly believes that by increasing the RISC-V community through dissemination, it will strongly contribute to the quality and reliability of the IP blocks developed in ISOLDE. Although TRL6 is foreseen as endpoint, a large stakeholder community can help identify bugs, improve functionality, and enhance the overall quality and reliability of the project. This dissemination plan will describe the methodology and tools to be used to generate maximum dissemination impact.

30 April 2025

The ISOLDE project aims to significantly address the RISC-V growing demand: by the end of our project, we will have high-performance RISC-V processing systems and platforms at least at Technology Readiness Level (TRL) 7 for the vast majority of the proposed architecture components, with the expectation that 2 years after project completion, ISOLDE’s high-performance components will be used in industrial quality products. Moreover, the project extends its expertise to the realm of computing by spearheading the development of multi-precision Vector processing units integrated with RISC-V cores. This initiative seeks to enhance computing efficiency for specific applications while furnishing Europe and the open-source community with innovative solutions to computational challenges.

This document describes the virtual repositories of ISOLDE IP as a summarizing work performed within ISOLDE WP6 – Open – source Strategy, Business Models, Exploitation and Dissemination in Task 6.1. A consolidated version of this Deliverable provides information and can demonstrate that networking within the realm of RISC-V, open-source technology, embedded processor development, and SoC application design can greatly expand ISOLDE reach and impact.

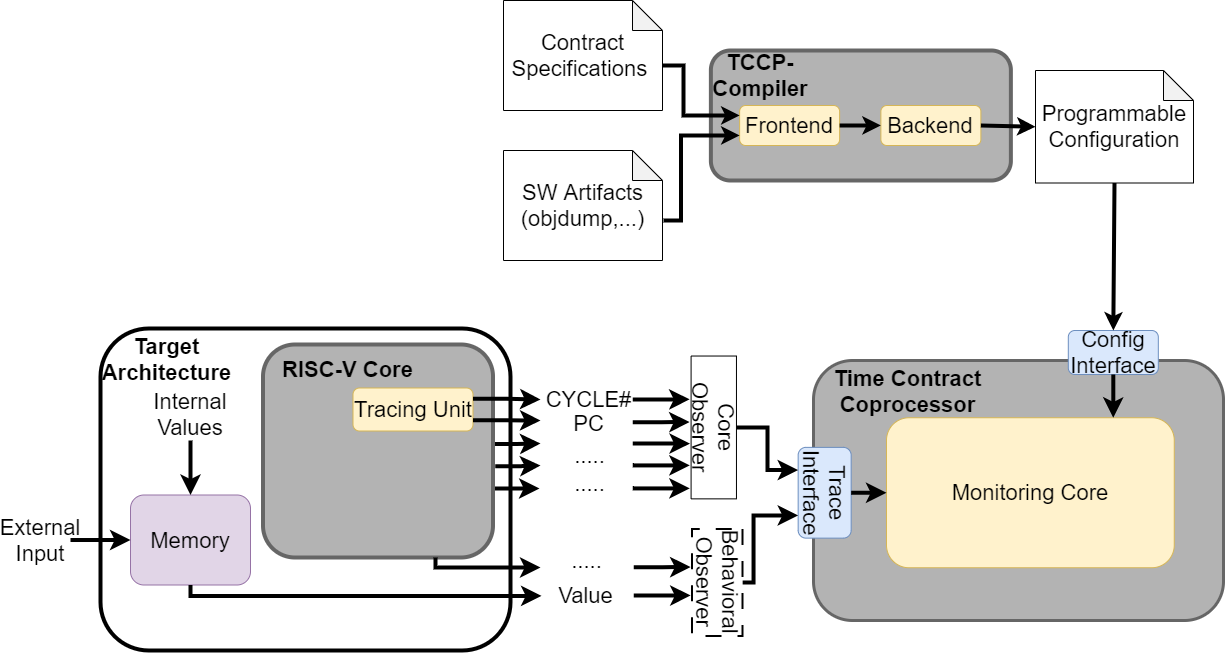

OFFIS is developing an open source on-chip co-processor for RISC-V processors to enable high-speed, high-resolution monitoring of timing and behavioral properties on a larger scale than is currently possible. The co-processor allows monitoring of complex application-level processors with full cycle accuracy.

In the design flow of safety-critical applications, the specification of strict timing properties and behavioral guarantees is crucial. One well-known specification method is Contract-Based Design using assume-guarantee contracts. A system model containing such contracts provides a perfect basis for deriving run-time monitor specifications automatically. These specifications are then executed by our newly designed co-processor to achieve continuous monitoring of safety-relevant properties even in large-scale and dynamically evolving applications.

The mentioned contracts supervise various safety requirements covering functional and non-functional properties such as timing, temperature ranges or software parameters. This allows monitoring that a specific controller maintains a parameter within a defined range over a specified time frame, such as running closed-loop motor control parallel to the execution of a specific resource-heavy task, or that a complex AI algorithm always completes its execution within a specified period.

Our contract-based runtime monitoring approach consists of three interacting components:

At its core, the Time Contract Co-Processor (TCCP) connects to two other components, the TCCP-Compiler and the observer interfaces.

The TCCP executes contract-based specifications in hardware, it observes various event sources via an observer interface. The observers are minimalistic adapters to source data, like a RISC-V trace port to observe computational progress or a memory content observer. The TCCP monitors events according to its programmable configuration derived from contract specifications. These specifications are processed by the TCCP compiler, which generates a configuration program for the TCCP. The coprocessor is specifically designed to allow high monitoring capacity and cycle-accurate temporal resolution. Furthermore, enabling updateable contracts via the compiler provides a substantial increase in flexibility over existing statically configured hardware-monitoring approaches.

About OFFIS

OFFIS, an affiliated institute of the Carl von Ossietzky Universität Oldenburg, has been transforming scientific expertise in computer science into innovations since its founding in 1991. These innovations are further developed into marketable products by industrial partners.

The OFFIS production division focuses on the digital transformation of traditional production systems and processes, aiming to achieve various goals. These include improving the efficiency of individual processes or production steps in assembly lines, enabling better cooperation between different machines, enhancing availability through predictive maintenance, and improving quality through error detection during manufacturing.

The ISOLDE consortium recently gathered in Munich on February 11-12, 2025, for a progress project meeting, bringing together partners from across Europe both in person and online. Hosted by HM Hochschule München University of Applied Sciences, this meeting was a proof of the collective expertise, dedication, and collaboration driving ISOLDE forward in its mission to develop high-performance RISC-V processing systems for key sectors such as automotive, space, and IoT.

Over two days of discussions and strategic alignment, the consortium members shared updates on their progress and defined the next steps to accelerate ISOLDE’s objectives. Work package leaders presented significant advancements in areas such as open-source IP core enhancement, system software development, and the integration of accelerators and extensions. Their contributions reflected the commitment and hard work of every member of the consortium involved in the project.

One of the most valuable aspects of the meeting were the workshops, in which partners came together to tackle technical challenges and explore new solutions. These sessions highlighted the strength of ISOLDE’s multidisciplinary approach, leveraging the diverse expertise within the consortium. The open exchange of ideas and knowledge reinforced the strong partnership that is essential for the project's success.

The success of this meeting would not have been possible without the active participation and engagement of all consortium members. A big thank you to everyone who contributed their time, expertise, and enthusiasm—whether attending in person or virtually. The ISOLDE’s consortium dedication is what makes this project a truly collaborative and forward-thinking initiative.

As we continue towards our shared goal of delivering customizable, high-performance IPs hosted on European servers, we look forward to further strengthening our partnerships and achieving new milestones together.

Stay tuned for more updates as ISOLDE continues!

The TRISTAN and ISOLDE projects are working closely together on establishing RISC-V processor technology in Europe. The results of the projects are planned to complement each other. Each project focuses on a different performance class. Both projects’ consortia are composed of partners from industry (both large industries as well as SMEs), research and RISC-V related industry associations.

We are delighted to share the highlights from the latest ISOLDE project meeting, which took place on July 17th and 18th in the city of Bucharest, Romania. This meeting was a key step in the project development as all project partners gathered the appointment either in person or remotely.

During the two-day event, our consortium reviewed the latest updates and advancements within the project. Our discussions focused on the feedback of the previous review meeting in Brussels to refine the technical progress and sharing insights that will drive the ISOLDE project forward. The commitment and dedication of each partner were evident, as all partners collectively navigated through the different challenges that this project proposes.

Additionally, the attendants to this event had the chance to share time with the whole consortium and network to find synergies between all of them.

We are excited about the future of the ISOLDE project and the positive impact it will have in the industry. The productive discussions and renewed energy from this meeting have set a strong foundation for our upcoming phases.

Thank you to all the partners for their active participation and continuous commitment. Stay tuned for more updates as we continue to advance and achieve our project goals.

ISOLDE's open access publications are available at https://zenodo.org/communities/isolde.

Synergistic memory optimisations: precision tuning in heterogeneous memory hierarchies, Gabriele Magnani 1, Daniele Cattaneo 1, Lev Denisov 1, Giuseppe Tagliavini 1, Giovanni Agosta 1, Stefano Cherubin 1, G. Magnani 1, D. Cattaneo 1, L. Denisov 1, G. Tagliavini 2, G. Agosta 1 and S. Cherubin 3; 1 DEIB, Politecnico di Milano, Milan, Italy; 2 DISI, University of Bologna, Bologna, Italy; 3 IDI, NTNU, Trondheim, Norway., IEEE TRANSACTIONS ON COMPUTERS, VOL. XX, NO. X, AUGUST 202X

AraXL: A Physically Scalable, Ultra-Wide RISC-V Vector Processor Design for Fast and Efficient Computation on Long Vectors, Navaneeth Kunhi Purayil, Matteo Perotti, Tim Fischer, Luca Benini, DATE 2025 Conference, https://arxiv.org/abs/2501.10301

Ramping Up Open-Source RISC-V Cores: Assessing the Energy Efficiency of Superscalar, Out-of-Order Execution,Computing Frontiers 2025

CVA6-VMRT: A Modular Approach Towards Time-Predictable Virtual Memory in a 64-bit Application Class RISC-V Processor, Christopher Reinwardt, Robert Balas, Alessandro Ottaviano, Angelo Garofalo, Luca Benini, Computing Frontiers 2025

AraOS: Analyzing the Impact of Virtual Memory Management on Vector Unit Performance, Mateo Perotti, Vincenzo Maisto, Moritz Imfeld, Nils Wistoff, Alessandro Cilardo, Luca Benini, Computing Frontiers 2025

The ISOLDE Space Demonstrator: A Platform for AI Applications on Satellites, Emanuele Valpreda, Roberto Morelli, Antonio Sciarappa, Davide Di Ienno, Carlo Ciancarelli, Paolo Serri, Valeria Parascandolo, antonio leboffe, Dario Pascucci, Daniele Gregori, Mattia Paladino, Daniele Jahier Pagliari, Alessio Burrello, Sara Vinco, Gianvito Urgese, Maurizio Martina, Guido Masera, William Fornaciari, Federico Reghenzani, Andrea Galimberti, Giovanni Agosta, Davide Zoni, Andrea Acquaviva, Francesco Conti, RISC-V in Space Workshop

Expanding SafeSU capabilities by leveraging security frameworks for contention monitoring in complex SoCs, Pablo Andreu, Sergi Alcaide, Pedro Lopez, Jaume Abella, Carles Hernández, Future Generation Computer Systems, https://www.sciencedirect.com/science/article/pii/S0167739X24004825

Model Predictive Control Acceleration on RISC-V, Martin Kostal, NXP Semiconductors, Poster, HiPeac 2025

SIMD Extensions – A Historical Perspective, Diana Vuta-Popescu, Ionut, Catalin Antofi, Catalin Bogdan Ciobanu, Csaba Zoltan Kertesz, 2024 IEEE 30th International Symposium for Design and Technology in Electronic Packaging (SIITME)

TIE Micro – Chiplets and Next-gen Packaging, Catalin Bogdan Ciobanu, Dan Manolescu, Roxana Vladuta, Luciana Chitu, Cosmin Moisa, Marcel Manofu, Paul Svasta, 2024 IEEE 30th International Symposium for Design and Technology in Electronic Packaging (SIITME)

Systolic Array Matrix Multiplication Accelerator, Alexandru Puscasu, Catalin Bogdan Ciobanu, Octavian Buiu, International Semiconductor Conference (CAS)

Spatzformer: An Efficient Reconfigurable Dual-Core RISC-V V Cluster for Mixed Scalar-Vector Workloads, Matteo Perotti†, Michele Raeber†, Mattia Sinigaglia*, Matheus Cavalcante†, Davide Rossi*, Luca Benini†*, †ETHZ (ETH Zurich, Switzerland), *UNIBO (Universita' di Bologna, Italy), ASAP 2024 Conference, https://arxiv.org/abs/2407.05447

RISC-V Accelerators, Enablement and Applications for Automotive and Smart Home in the ISOLDE Project, Cătălin Bogdan Ciobanu, Honorius Gâlmeanu, Alexandru Puscasu, Mihai Gologanu, Octavian Buiu, Mihai Antonescu, Vlad-Gabriel Serbu, Vasile-Mădălin Moise, Cristian-Tiberius Axinte, Alexandru-Tudor Popovici, George-Iulian Uleru, Andrei Stan, Mihai Munteanu, Alexandru Drîmbărean, Csaba Nemeti, Dănut Rotar, Cosmin Moisa, Bogdan Ditu, Petre Cristian Trusca, Marius Antache, Simona Costinescu, Mari-Anais Sachian, George Suciu, Cristian Gheorghe, Cristina Tudor, Kejsi Koci, International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS) 2024 conference

Integration and Optimization of EV Charging Processes in a Decentralized Local Energy Trading Market, Christoph Groß; Tin Stribor Sohn; Oliver Bringmann, 2024 IEEE International Conference on Omni-layer Intelligent Systems (COINS), https://www.researchgate.net/publication/383162902_Integration_and_Optim...

Onchip Traffic Injection to Counteract Timing Side-Channel Attacks, Francisco Fuentes, Sergi Alcaide, Raimon Casanova, Jaume Abella; †Barcelona Supercomputing Center (BSC) ‡Microelectronic and Electronic Systems Department, Barcelona, Spain Universitat Aut`onoma de Barcelona (UAB), Bellaterra, Spain, Embedded Real Time Systems (ERST) 2024 conference, https://hal.science/hal-04614786

RISC-V on mixed-critical platforms (poster + published extended abstract), Samuel Ardaya-Lieb, Holger Blasum, Enkhtuvshin Janchivnyambuu, Florian Krebs, Jan Reinhard, Darshak Sheladiya and George Violettas, RISC-V Summit Munich 2024, https://www.sysgo.com/fileadmin/user_upload/data/blog/SYSGO_2024-06_Mixe...

Hardware Acceleration for High-Volume Operations of CRYSTALS-Kyber and CRYSTALS-Dilithium, Xavier Carril, Charalampos Kardaris, Jordi Ribes-González, Oriol Farràs, Carles Hernandez, Vatistas Kostalabros, Joel Ulises González-Jiménez, Miquel Moretó, ACM Transactions on Reconfigurable Technology and Systems, https://dl.acm.org/doi/abs/10.1145/3675172

SETHET – Sending Tuned numbers over DMA onto Heterogeneous clusters: an automated precision tuning story, Gabriele Magnani1, Daniele Cattaneo1, Lev Denisov1, Giuseppe Tagliavini2, Giovanni Agosta1, Stefano Cherubin3; 1 Politecnico di Milano (Italy), 2 University of Bologna (Italy), 3 NTNU (Norway), ACM Computing Frontiers 2024

Siracusa: A 16 nm Heterogenous RISC-V SoC for Extended Reality With At-MRAM Neural Engine, Arpan Suravi Prasad, Moritz Scherer, Francesco Conti, Davide Rossi, Alfio Di Mauro, Manuel Eggimann, Jorge Tomas Gomez, Ziyun Li, Syed Shakib Sarwar, Zhao Wang, Barbara De Salvo, Luca Benini, IEEE Journal of Solid-State Circuits, https://hdl.handle.net/11585/953203

Accelerating WebAssembly Interpreters in Embedded Systems through Hardware-Assisted Dispatching, Matthias Rupp, Stefan Wallentowitz, ARCS Conference 2024

The European Chips Act, The ISOLDE Project, and Open-Source Hardware, Willibald Krenn; Andrew Wilson; Ambily Suresh; Manuel Freiberger (Silicon Austria Labs, Graz), 2024 Argentine Conference on Electronics (CAE)

MX: Enhancing RISC-V’s Vector ISA for Ultra-Low Overhead, Energy-Efficient Matrix Multiplication, Matteo Perotti†, Yichao Zhang†, Matheus Cavalcante†, Enis Mustafa†, Luca Benini†*, †ETHZ (ETH Zurich, Switzerland), *UNIBO (Universita' di Bologna, Italy), DATE 2024 Conference, https://arxiv.org/pdf/2401.04012.pdf

A Model-Driven Architecture Approach to Efficient and Adaptable Software Code Generation, Mayuri Bhadra, Daniel Albert, Ungsang Yun, Robert Kunzelmann, Daniela Sanchez Loperera and Wolfgang Ecker, Infineon Technologies AG, Munich, MBMV 2024 Proceedings, https://ieeexplore.ieee.org/document/10564525

A Comparative Analysis of ARM and RISC-V ISAs for Deeply Embedded Systems, Natalie Simson, Ares Tahiraga and Wolfgang Ecker, Infineon Technologies AG, Munich, MBMV 2024 Proceedings, https://ieeexplore.ieee.org/document/10564506

Black-Box IP Validation with the SafeTI Traffic Injector: A Success Story, Francisco Fuentes, Sergi Alcaide, Raimon Casanova, Jaume Abella, IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), 2023, http://hdl.handle.net/2117/397442

SafeLS: An Open Source Implementation of a Lockstep NOEL-V RISC-V Core, Marcel Sarraseca, Sergi Alcaide, Francisco Fuentes, Juan Carlos Rodriguez, Feng Chang, Ilham Lasfar, Ramon Canal, Francisco J. Cazorla, Jaume Abella, IEEE 29th International Symposium on On-Line Testing and Robust System Design (IOLTS), 2023, http://hdl.handle.net/2117/393235

RISC-V Processor Technologies for Aerospace Applications in the ISOLDE Project, William Fornaciari, Federico Reghenzani, Giovanni Agosta, Davide Zoni, Andrea Galimberti, Francesco Conti, Yvan Tortorella, Emanuele Parisi, Francesco Barchi, Andrea Bartolini, Andrea Acquaviva, Daniele Gregori, Salvatore Cognetta, Carlo Ciancarelli, Antonio Leboffe, Paolo Serri, Alessio Burrello, Daniele Jahier Pagliari, Gianvito Urgese, Maurizio Martina, Guido Masera, Rosario DiCarlo, and Antonio Sciarappa, 1 Politecnico di Milano, Milano, Italy, 2 University of Bologna, Bologna, Italy, 3 E4 Computer Engineering SpA, Italy, 4 Thales Alenia Space Italia S.p.A., Italy, 5 Politecnico di Torino, Torino, Italy, 6 Leonardo SpA, Italy, International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS) 2023 conference, https://re.public.polimi.it/retrieve/ceb20d00-33d1-41df-8a37-1870b06ea92...

Envisioning a Safety Island to Enable HPC Devices in Safety-Critical Domains, Jaume Abella, Francisco J. Cazorla, Sergi Alcaide, Michael Paulitsch, Yang Peng, Inês Pinto Gouveia, (white paper), https://arxiv.org/abs/2307.11940

Last week, the ISOLDE consortium completed its 18-month review to share the latest advancements of the project with the European Commission. The collaboration of all participants provided valuable insights making the session a place for showing the progress of the project and sharing feedback.

This meeting represented a significant milestone for the ISOLDE project, aimed at developing advanced RISC-V processing systems to enhance European industries. Accomplishing this objective holds the potential to revolutionize key sectors in Europe, including automotive, aerospace, and IoT.

During three full days, ISOLDE’s partners dedicated their effort to analyse every element of their work, leaving no doubt about each point of the tasks they needed to discuss and strategizing the path forward.

The attendees at the meeting ranged from our Work Package leaders to some Task leaders and members from all 35 partner organizations, who brought their points of view both in-person in Brussels and remotely.

Moreover, presentations showcased at the event received positive feedback, confirming the dedication of all those involved in the project.

Following the review, the ISOLDE consortium gathered for an after-work social event, providing a welcome opportunity for participants to establish personal connections outside of the professional environment.

The ISOLDE project is growing stronger than ever as its partners continue to attain its goals together. Stay tuned to ISOLDE’s news through our website and social media channels and be aware of all our upcoming milestones!

One of the goals of ISOLDE is to strengthen the dissemination of RISC-V projects in Europe, and ISOLDE partner HM has taken a lead role here with the local organization of RISC-V Summit Europe 2024. It will be held in Munich from June 24 to June 28. As a literal “summit” it will bring together the entire community in Europe, including industry, academia and individual developers.

After the pandemic, there are now three RISC-V Summits around the globe, focusing on the key markets of RISC-V: RISC-V Summit North America, RISC-V Summit Europe and RISC-V Summit China. RISC-V Summit Europe is the joint effort of three key communities from France, Germany and Spain, together with RISC-V International. The steering and program committees include the variety of the European community. Compared to the other summits, Europe traditionally had a more research centric approach, which still reflects on the strong academic impact of the European ecosystem in this community. With over 180 submissions, the RISC-V Summit Europe is the place to present.

But with the rapid adoption of RISC-V in Europe, driven by that strong research ecosystem, we can see an increasing interest and participation from industry. At this year's RISC-V Summit Europe, for example, the CTO of Thales, Bernhard Quendt, will hold a keynote, accompanied by the SVP of Automotive Microcontrollers at Infineon, Thomas Böhm. The key person behind RISC-V, Krste Asanović, will present the State-of-the-Union of RISC-V. Other invited presenters include Alex Kocher, CEO of the Joint Venture Quintauris, and Johanna Bähr, Research Associate at Fraunhofer. Larry Wikelius, Director of the RISC-V Software Ecosystem (RISE) organization will give an update. And last but not least, the first batch of invited speakers includes Edward Wilford of Omdia, who as a Senior Principal Analyst will be speaking about RISC-V adoption in the microcontroller market and beyond.

The program will start on Monday with Technical Workgroup Meetings. The main program and expo will run from Tuesday to Thursday. Friday will be available for RISC-V focused projects to meet or disseminate their work. As RISC-V Summit Europe is the denoted “main summit” this year, the annual general meeting of all RISC-V members and an award ceremony will be part of the program.

About the HM:

Hochschule München (HM) is one of the largest universities of applied sciences in Germany. Their technical involvement in ISOLDE focuses on open-source CPU support for bytecode virtualization and an improved fault injection framework around the open-source tool Verilator. Beyond the technical contributions, HM is strongly involved in dissemination events. With HM professor Stefan Wallentowitz on the RISC-V board of directors, an impactful advocate of RISC-V is active in the ISOLDE project.